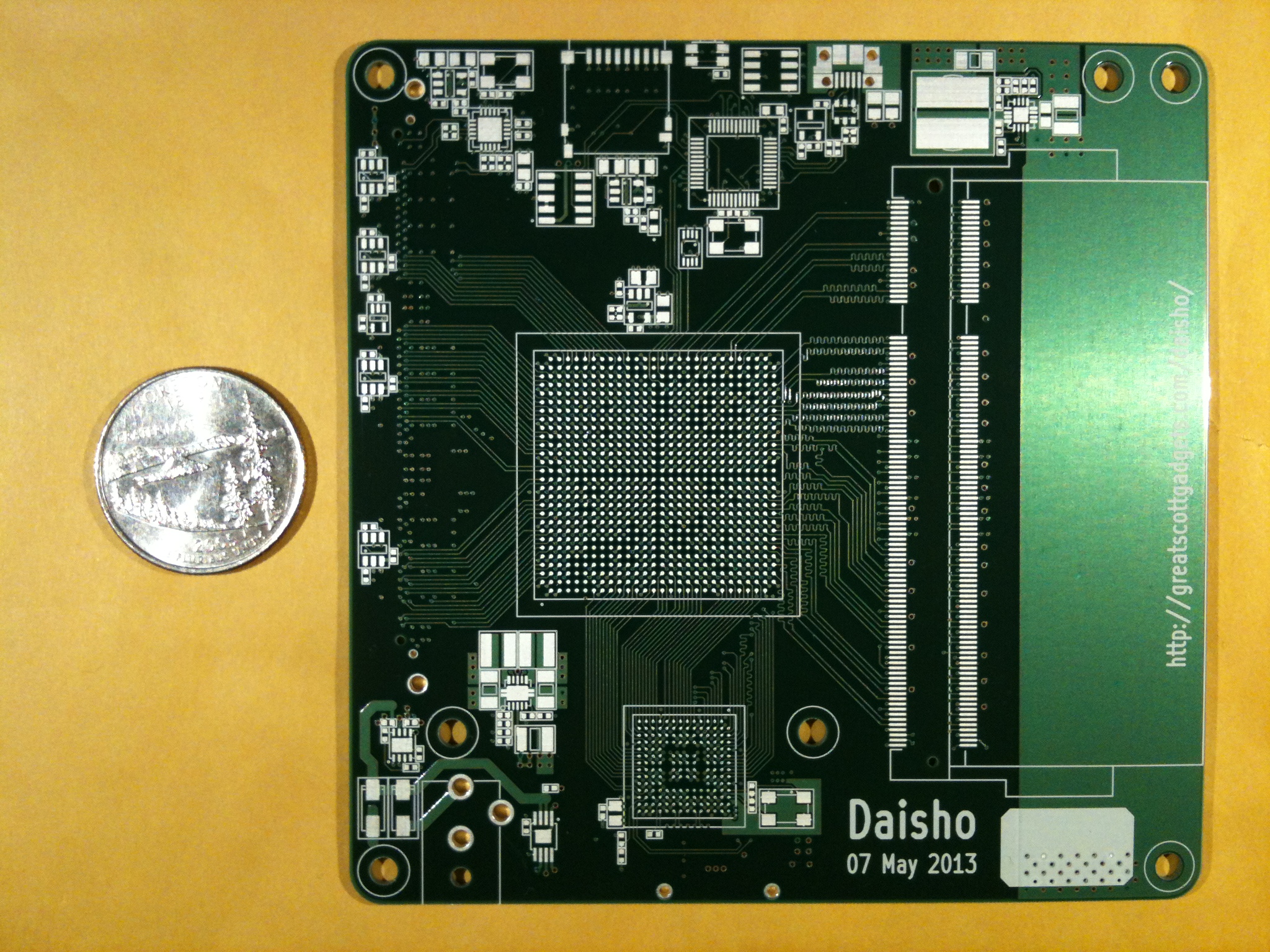

My First 8-Layer PCB

I recently completed my first 8-layer PCB design, for Michael Ossmann's [Daisho project][daisho-annouce]. Among the challenges: a 780-pin Altera Cyclone IV FPGA, a USB 3.0 chip with 0.8mm ball spacing, very high-speed parallel and serial buses, tight power constraints, and keeping the cost down. Oh, and did I mention I was using only open-source schematic and PCB tools (KiCAD)?

It's back from manufacturing, and the first few subsystems are being assembled. Any bets on whether it'll work the first time? :-)

Comments

So… did it work the first time?

@Carey Sonsino: Hey there! The answer is, "almost". Mike Ossmann, the project instigator, soldered together a board over the last couple of days, and so far there are no shorts, and the voltage supplies appear to function properly. Assessing the state of the FPGA and USB 3.0 PHY chips is another story. So he's sent me the assembled board, which I should receive Friday. At that point, I'll run some tests from the onboard FPGA using a Verilog project to exercise the various pins and peripherals and see what remaining soldering and logical (schematic and PCB) errors exist in the design.

Mike discovered a couple of glaring errors in the PCB design. I missed a subtle shift of 0.3mm between the two rows of pins on the DDR2 connector, but he was able to bend the pins (100 of them!) a little bit and solder them securely despite the error. And I thoughtlessly followed the pin numbering provided by the connector manufacturer of our JTAG/SWD connector, which it turns out is a mirrored numbering from what normal people do. So pins 1 and 2 are swapped, 3 and 4 are swapped, and so on… Mike was able to devise a cable that would adapt to this error.

So far, not bad for such a complex design. Still there's a lot of complexity remaining to be tested… I'll know more this weekend and in to the next week.

Do you guys have any tools to perform DRC checks for track length matching?

@pfalcon: I've built a kludgy Python script that parses the board file and calculates trace length. It also looks at the net class and layer number and computes delay based on my prop-delay estimates. I should publish that script somewhere, but it's really just a hack-ball right now. So my pride is preventing me from sharing it (and my embarrassment).